# **Deep Learning HDL Toolbox**<sup>™</sup> User's Guide

# MATLAB®

R

**R**2022**b**

#### **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Deep Learning HDL Toolbox<sup>™</sup> User's Guide

© COPYRIGHT 2020- 2022 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ {\tt products}\ {\tt are}\ {\tt protected}\ {\tt by}\ {\tt one}\ {\tt or}\ {\tt more}\ {\tt U.S.}\ {\tt patents}.\ {\tt Please}\ {\tt see}\ {\tt www.mathworks.com/patents}\ {\tt for}\ {\tt more}\ {\tt information}.$

#### **Revision History**

| Online only | New for Version 1.0 (Release 2020b)       |

|-------------|-------------------------------------------|

| Online only | Revised for Version 1.1 (Release R2021a)  |

| Online only | Revised for Version 1.2 (Release R2021b)  |

| Online only | Revised for Version 1.3 (Release R2022a)  |

| Online only | Revised for Version 1.4 (Release R2022b)  |

|             | Online only<br>Online only<br>Online only |

## What is Deep Learning?

| Introduction to Deep Learning | 1-2 |

|-------------------------------|-----|

| Training Process              |     |

| Training from Scratch         | 1-3 |

| Transfer Learning             | 1-3 |

| Feature Extraction            | 1-4 |

| Convolutional Neural Networks | 1-5 |

1

2

3

4

#### **Deep Learning Processor**

| Deep Learning Processor IP Core Architecture |

|----------------------------------------------|

| DDR Memory                                   |

| Memory Access Arbitrator Modules             |

| Convolution Kernel                           |

| Top-Level Scheduler Module                   |

| Fully Connected Kernel                       |

| Custom Kernel                                |

| Profiler Utilities                           |

## **Applications and Examples**

#### **Deep Learning on FPGA Overview**

| Deep Learning on FPGA Workflow                                                                                     | 4-2 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Deep Learning on FPGA Solution         Advantages of Deep Learning on FPGA         Deep Learning on FPGA Workflows | 4-4 |

| Prototype Deep Learning Networks on FPGA and SoC Devices                                                                                                                                                                                                                                                                   | 5-2                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Profile Inference Run                                                                                                                                                                                                                                                                                                      | 5-4                              |

| Multiple Frame Support         Input DDR Format         Output DDR Format         Manually Enable Multiple Frame Mode                                                                                                                                                                                                      | 5-7<br>5-7<br>5-7<br>5-8         |

| Initialize Deployed Deep Learning Processor Without Using a MATLAB         Connection       Prerequisites         Prerequisites       Generate File         Generate File       Generated File Structure         Initiate Deployed Deep Learning Processor IP Core       Initiate Deployed Deep Learning Processor IP Core | 5-9<br>5-9<br>5-9<br>5-9<br>5-13 |

#### Fast MATLAB to FPGA Connection Using LIBIIO/Ethernet

# 6

7

5

# LIBIIO/Ethernet Connection Based Deep Learning Network Deployment

|                             | 6-2 |

|-----------------------------|-----|

| Ethernet Interface          | 6-2 |

| LIBIIO/Ethernet Performance | 6-2 |

#### **Networks and Layers**

| Supported Networks, Layers, Boards, and Tools | 7-2  |

|-----------------------------------------------|------|

| Supported Pretrained Networks                 | 7-2  |

| Supported Layers                              | 7-13 |

|                                               | 7-31 |

|                                               | 7-31 |

|                                               | 7-31 |

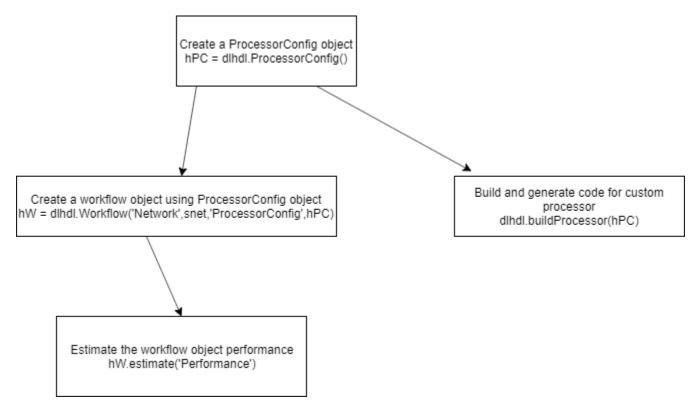

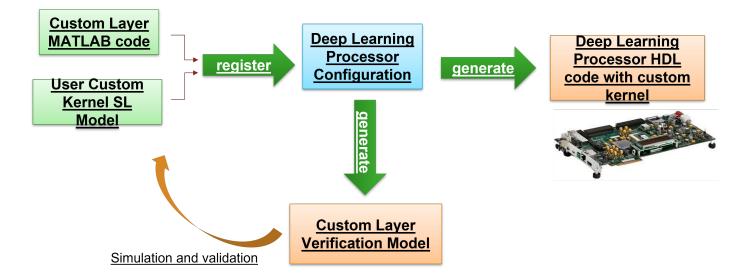

## **Custom Processor Configuration Workflow**

# 8

| Custom Processor Configuration Workflow                         | 8-2 |

|-----------------------------------------------------------------|-----|

| Estimate Performance of Deep Learning Network                   | 8-3 |

| Estimate Performance of Custom Deep Learning Network for Custom |     |

| Processor Configuration                                         | 8-3 |

| Evaluate Performance of Deep Learning Network on Custom Processor<br>Configuration                                                                                       | 8-4          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Estimate Resource Utilization for Custom Processor Configuration<br>Estimate Resource Utilization<br>Customize Bitstream Configuration to Meet Resource Use Requirements | 8-10<br>8-10 |

|                                                                                                                                                                          | 8-11         |

| Effects of Custom Deep Learning Processor Parameters on Performance<br>and Resource Utilization                                                                          | 8-17         |

| Generate Custom Bitstream to Meet Custom Deep Learning Network<br>Requirements                                                                                           | 8-19         |

| Create Deep Learning Processor Configuration for Custom Layers                                                                                                           | 8-26         |

| Deploy Custom Layer Networks                                                                                                                                             | 8-26         |

| Create a Deep learning Processor Configuration                                                                                                                           | 8-26         |

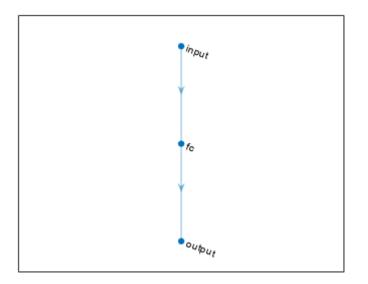

| Create Custom Layer MATLAB Function                                                                                                                                      | 8-27         |

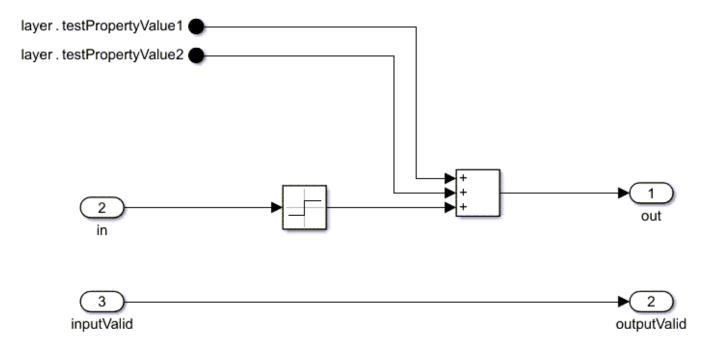

| Create Custom Layer Simulink Function                                                                                                                                    | 8-28         |

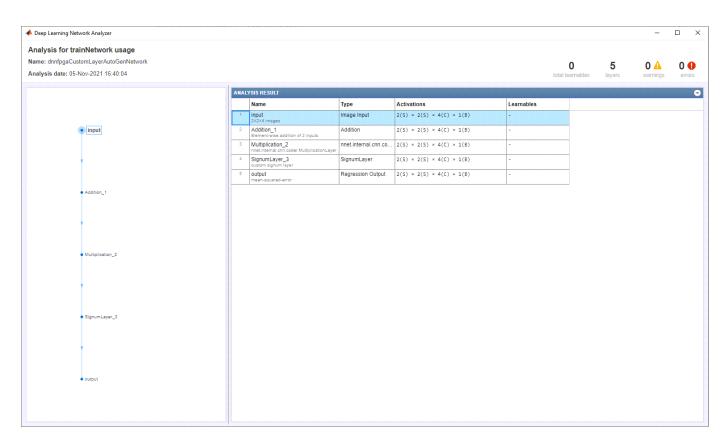

| Register Custom Layer and Model                                                                                                                                          | 8-28         |

| Generate Verification Model for Custom Layer                                                                                                                             | 8-29         |

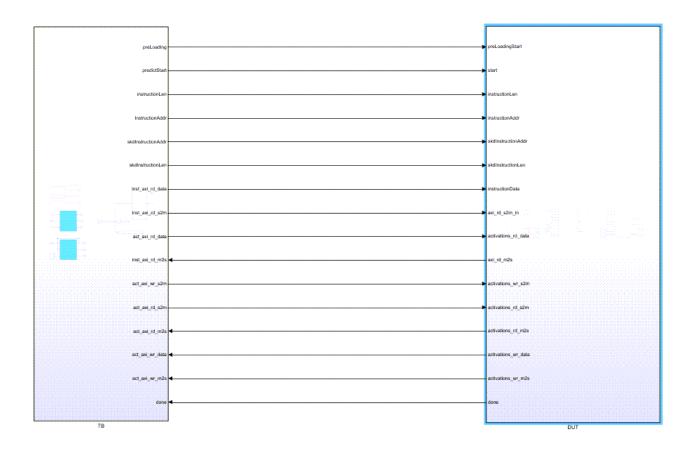

| Simulate and Validate Custom Layer Model                                                                                                                                 | 8-31         |

| Generate Custom Bitstream                                                                                                                                                | 8-32         |

| Deploy and Predict Custom Layer Network on Hardware                                                                                                                      | 8-32         |

| Custom Layer Registration File                                                                                                                                           | 8-32         |

| Register, Validate, and Deploy Custom Natural Logarithm Layer Network<br>to FPGA                                                                                         | 8-35         |

# **Custom Processor Code Generation Workflow**

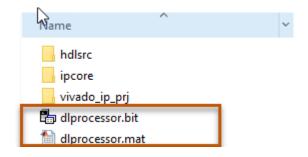

| Generate Custom Bitstream    | 9-2 |

|------------------------------|-----|

| Generate Custom Processor IP | 9-3 |

## **Featured Examples**

| 1 | Λ |

|---|---|

| ┻ | υ |

9

| Get Started with Deep Learning FPGA Deployment on Intel Arria 10 SoC | 10-3  |

|----------------------------------------------------------------------|-------|

| Get Started with Deep Learning FPGA Deployment on Xilinx ZCU102 SoC  | 10-6  |

| Get Started with Deep Learning FPGA Deployment on Xilinx ZC706 SoC   | 10-10 |

| Logo Recognition Network                                             | 10-13 |

| Deploy Transfer Learning Network for Lane Detection                                                                                                                                                                                       | 10-17                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

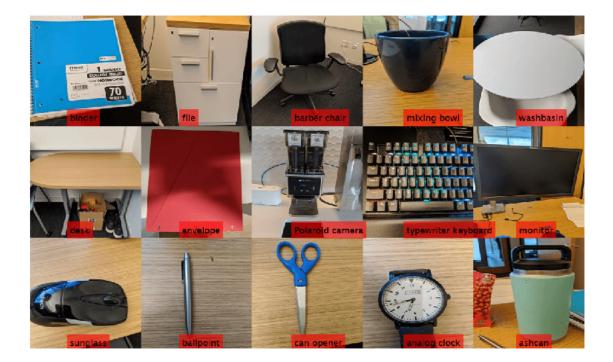

| Image Category Classification by Using Deep Learning                                                                                                                                                                                      | 10-21                                |

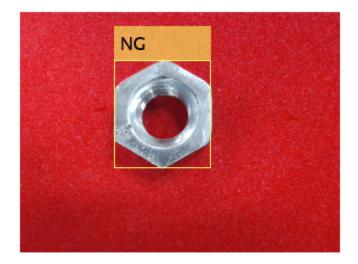

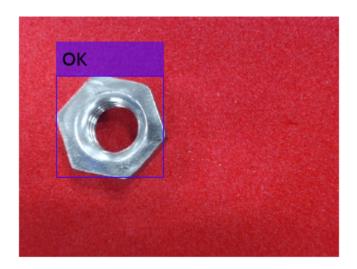

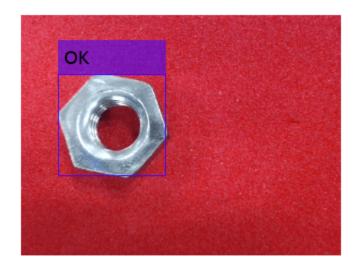

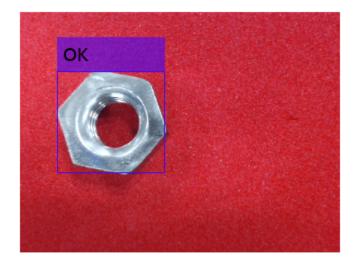

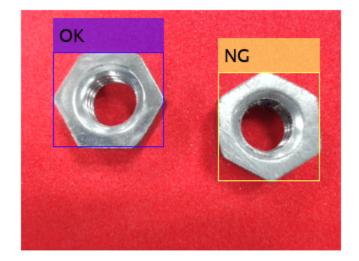

| Defect Detection                                                                                                                                                                                                                          | 10-30                                |

| Profile Network for Performance Improvement                                                                                                                                                                                               | 10-47                                |

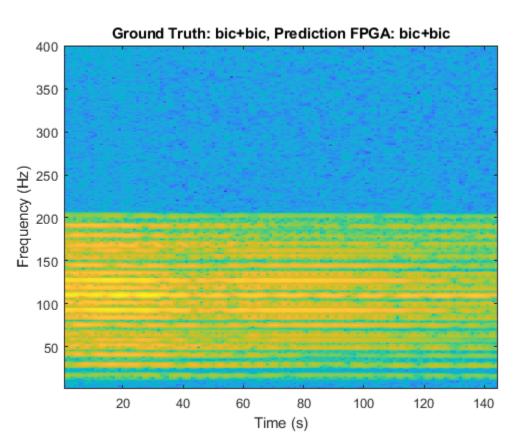

| Bicyclist and Pedestrian Classification by Using FPGA                                                                                                                                                                                     | 10-51                                |

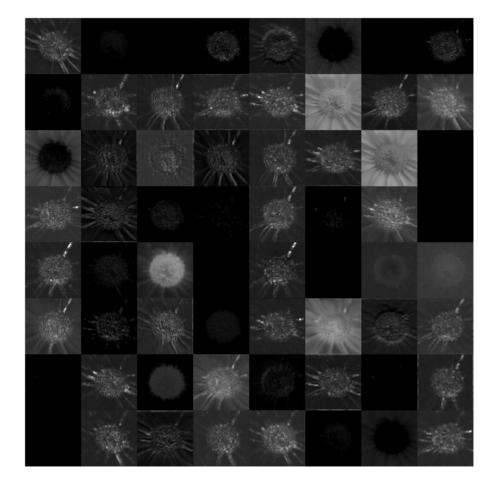

| Visualize Activations of a Deep Learning Network by Using LogoNet $\ .$                                                                                                                                                                   | 10-56                                |

| Authoring a Reference Design for Live Camera Integration with DeepLearning Processor IP Core                                                                                                                                              | 10-62                                |

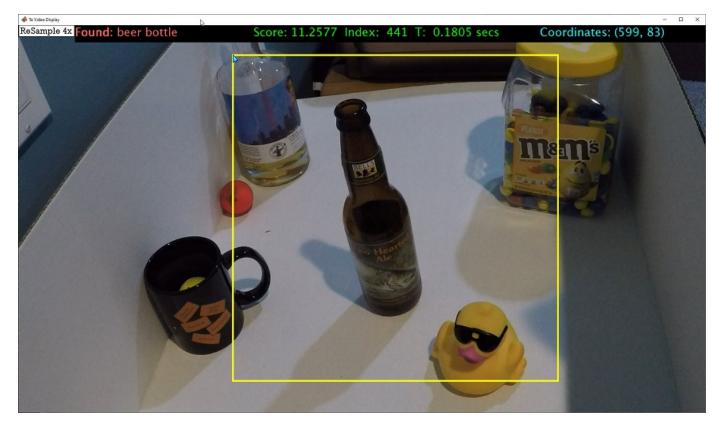

| Run a Deep Learning Network on FPGA with Live Camera Input                                                                                                                                                                                | 10-67                                |

| Running Convolution-Only Networks by Using FPGA Deployment                                                                                                                                                                                | <b>10-77</b>                         |

| Accelerate Prototyping Workflow for Large Networks by Using Ethernet                                                                                                                                                                      | 10-82                                |

| Create Series Network for Quantization                                                                                                                                                                                                    | 10-90                                |

| Custom Deep Learning Processor Generation to Meet Performance<br>Requirements                                                                                                                                                             | 10-94                                |

| Deploy Quantized Network Example                                                                                                                                                                                                          | 10-100                               |

| Deploy INT8 Network to FPGA                                                                                                                                                                                                               | 10-112                               |

| Evaluate Performance of Deep Learning Network on Custom Processor<br>Configuration                                                                                                                                                        | 10-119                               |

| Customize Bitstream Configuration to Meet Resource Use Requirements                                                                                                                                                                       | s<br>10-125                          |

| Vehicle Detection Using DAG Network Based YOLO v2 Deployed to FPGA                                                                                                                                                                        | 10-131                               |

| Customize Bitstream Configuration to Meet Resource Use Requirements                                                                                                                                                                       | 5                                    |

|                                                                                                                                                                                                                                           | 10-140                               |

|                                                                                                                                                                                                                                           |                                      |

| Image Classification Using DAG Network Deployed to FPGA                                                                                                                                                                                   | 10-140                               |

| Image Classification Using DAG Network Deployed to FPGA                                                                                                                                                                                   | 10-140<br>10-146                     |

| Image Classification Using DAG Network Deployed to FPGAClassify Images on an FPGA Using a Quantized DAG NetworkClassify ECG Signals Using DAG Network Deployed to FPGAPrototype and Verify Deep Learning Networks Without Target Hardware | 10-140<br>10-146<br>10-154<br>10-167 |

| Estimate Resource Utilization for Custom Board and Reference Design                            | 10-198      |

|------------------------------------------------------------------------------------------------|-------------|

|                                                                                                | 10-190      |

| Speech Command Recognition by Using FPGA                                                       | 10-201      |

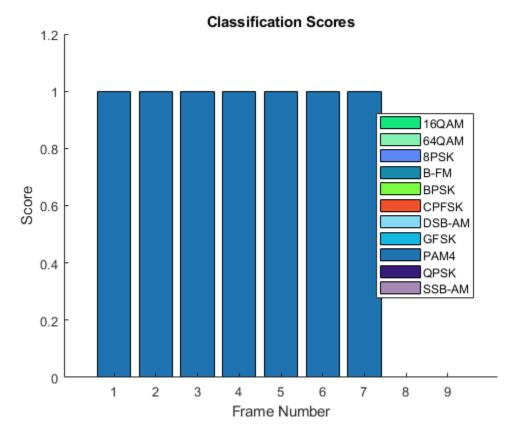

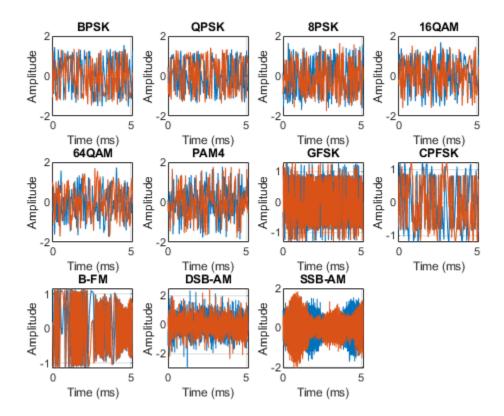

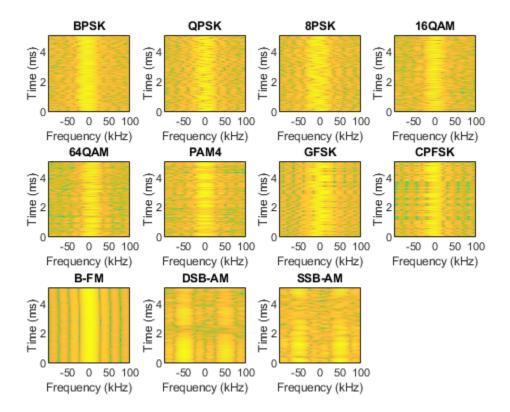

| Modulation Classification by Using FPGA                                                        | 10-211      |

| Deploy Simple Adder Network by using MATLAB Deployment Script and Deployment Instructions File | 1<br>10-223 |

| Human Pose Estimation by Using Segmentation DAG Network Deployed to FPGA                       | 1<br>10-231 |

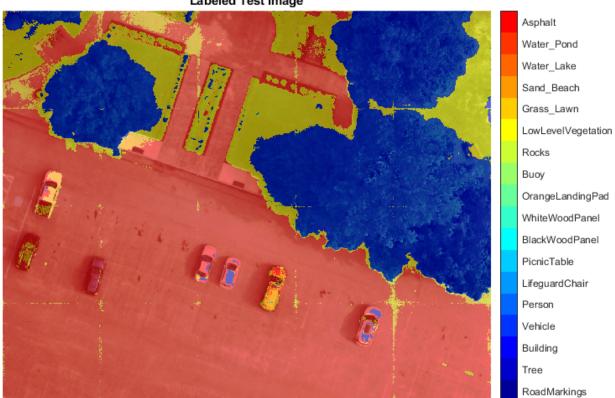

| Semantic Segmentation of Multispectral Images by Using Quantized U-<br>Net on FPGA             | 10-237      |

| Optimize Deep Learning Processor Configuration for Network<br>Performance                      | 10-246      |

| Run Sequence-to-Sequence Classification on FPGAs by Using DeepLearning HDL Toolbox             | 10-253      |

| Generate Word-By-Word Text on FPGAs by Using Deep Learning HDL<br>Toolbox                      | 10-260      |

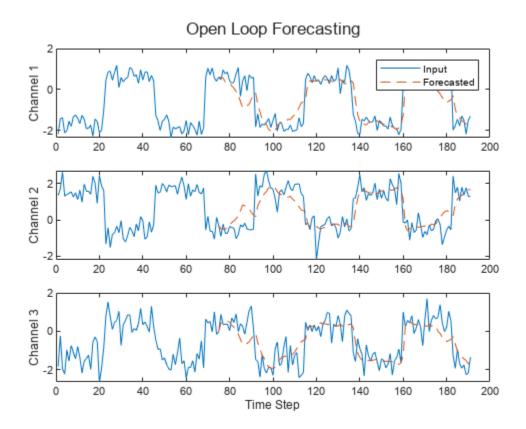

| Run Sequence Forecasting on FPGA by Using Deep Learning HDL<br>Toolbox™                        | 10-267      |

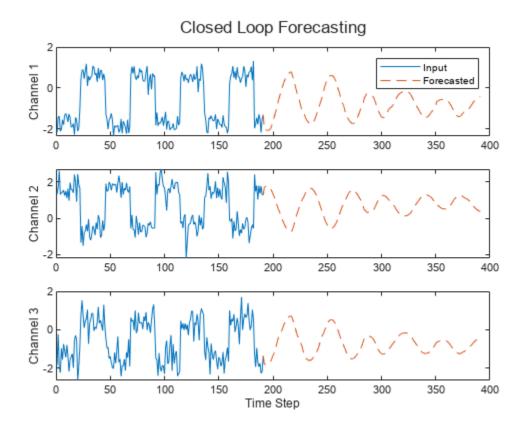

| Detect Objects Using YOLO v3 Network Deployed to FPGA                                          | 10-276      |

# 11

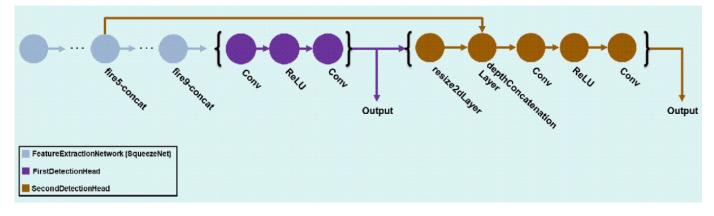

| Quantization of Deep Neural Networks | 11-2 |

|--------------------------------------|------|

| Precision and Range                  | 11-2 |

| Histograms of Dynamic Ranges         | 11-2 |

| Quantization Workflow Prerequisites  | 1-10 |

|                                      | 1-10 |

| Supported Networks and Layers 1      | 1-10 |

| Prerequisites for Calibration 1      | 1-10 |

|                                      | 1-11 |

|                                      | 1-11 |

| Calibration                          | 1-13 |

|                                      | 1-13 |

| Validation                           | 1-15 |

|                                      | 1-15 |

| Code Generation and Deployment 1     | 1-18 |

**Deep Learning Quantization**

| Generate Custom Generic Deep Learning Processor IP Core     | 12-2  |

|-------------------------------------------------------------|-------|

| Deep Learning Processor IP Core                             | 12-5  |

| Use the Compiler Output for System Integration              | 12-6  |

| External Memory Address Map                                 | 12-6  |

| Compiler Optimizations                                      | 12-6  |

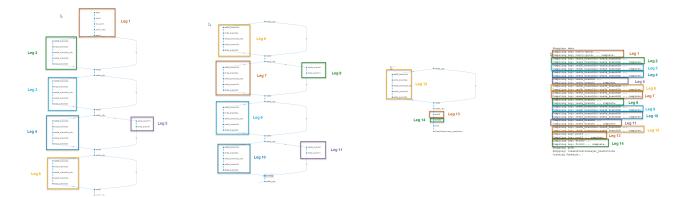

| Leg Level Compilations                                      | 12-7  |

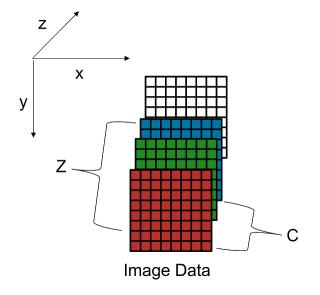

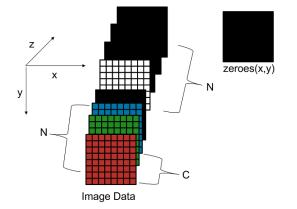

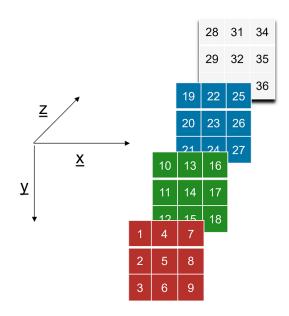

| External Memory Data Format                                 | 12-9  |

| Key Terminology                                             | 12-9  |

| Convolution Module External Memory Data Format              | 12-9  |

| Fully Connected Module External Memory Data Format          | 12-12 |

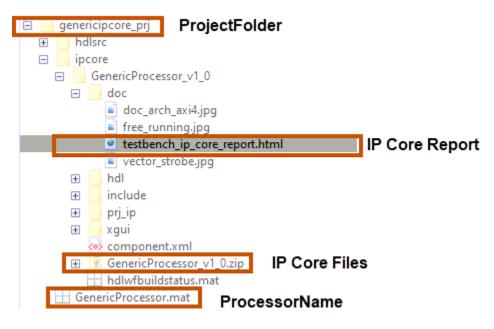

| Deep Learning Processor IP Core Report                      | 12-14 |

| Summary                                                     | 12-14 |

| Target Interface Configuration                              | 12-14 |

| Register Address Mapping                                    | 12-14 |

| IP Core User Guide                                          | 12-15 |

| IP Core File List                                           | 12-15 |

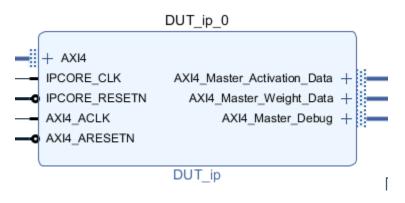

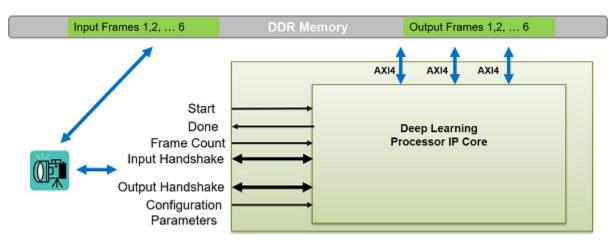

| Interface with the Deep Learning Processor IP Core          | 12-17 |

| Create Deep Learning Processor Configuration                | 12-17 |

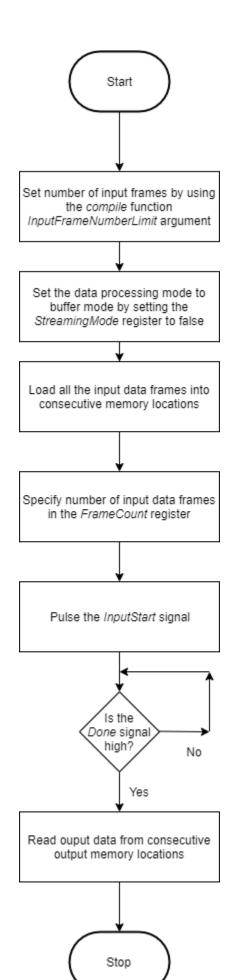

| Select Data Processing Mode                                 | 12-17 |

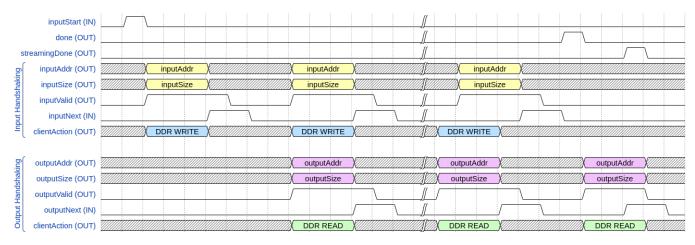

| Design Processing Mode Interface Signals                    | 12-18 |

| Design Batch Processing Mode Interface                      | 12-23 |

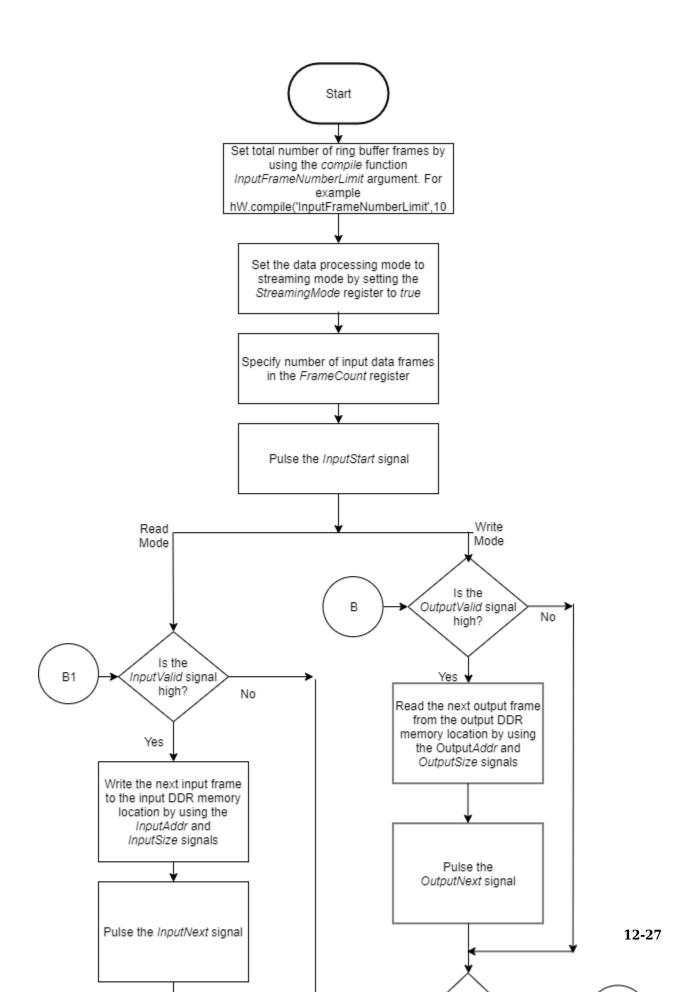

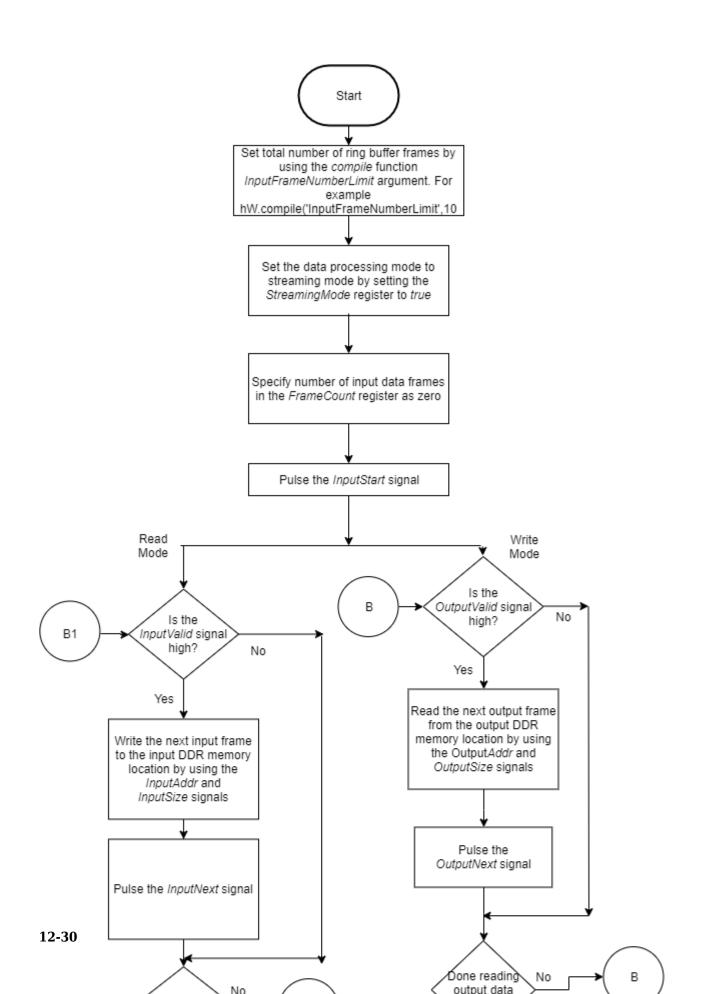

| Design Streaming Mode Interface                             | 12-25 |

| Access Data from DDR                                        | 12-31 |

| Deep Learning Processor IP Core Generation for Custom Board | 12-33 |

## **Deep Learning HDL Toolbox Support for LSTM Networks**

# 13

| Support for Long Short-Term Memory Networks Prediction and Forecasting |              |  |

|------------------------------------------------------------------------|--------------|--|

| How Deep Learning HDL Toolbox Compiles the LSTM Layer                  | 13-5         |  |

| LSTM Layer Architecture                                                | 13-5<br>13-6 |  |

12

# What is Deep Learning?

- "Introduction to Deep Learning" on page 1-2

- "Training Process" on page 1-3

- "Convolutional Neural Networks" on page 1-5

# **Introduction to Deep Learning**

Deep learning is a branch of machine learning that teaches computers to do what comes naturally to humans: learn from experience. The learning algorithms use computational methods to "learn" information directly from data without relying on a predetermined equation as model. Deep learning uses neural networks to learn useful representations of data directly from images. It is a specialized form of machine learning that can be used for applications such as classifying images, detecting objects, recognizing speech, and describing the content. The relevant features are automatically extracted from the images. The deep learning algorithms can be applied to supervised and unsupervised learning. These algorithms scale with data, that is, the performance of the network improves with size of the data.

# **Training Process**

You can train deep learning neural networks for classification tasks by using methods such as training from scratch, or by transfer learning, or by feature extraction.

### **Training from Scratch**

Training a deep learning neural network from scratch requires a large amount of labeled data. To create the network architecture by using Neural Network Toolbox<sup>™</sup>, you can use the built-in layers, define your own layers, or import layers from Caffe models. The neural network is then trained by using the large amounts of labeled data. Use trained network for predicting or classifying the unlabeled data. These networks can take few days or couple of weeks to train. Therefore, it is not a commonly used method for training networks.

For more information, see "Get Started with Transfer Learning".

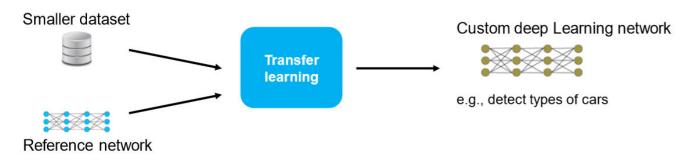

#### **Transfer Learning**

Transfer learning is used for cases where there is lack of labeled data. The existing network architectures, trained for scenarios with large amounts of labeled data, are used for this approach. The parameters of pretrained networks are modified to fit the unlabeled data. Therefore, transfer learning is used for transferring knowledge across various tasks. You can train or modify these networks faster so it is the most widely used training approach for deep learning applications.

For more information, see "Get Started with Transfer Learning"

#### **Feature Extraction**

Layers in deep learning networks are trained for extracting features from the input data. This approach uses the network as a feature extractor. The features extracted after the training process can be put into various machine learning models such as Support Vector Machines (SVM).

# **Convolutional Neural Networks**

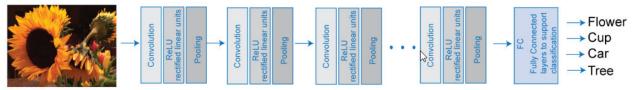

Convolutional neural networks (CNNs) are one of the most commonly used deep learning networks.They are feedforward artificial neural networks inspired by the animal's visual cortex. These networks are designed for data with spatial and temporal information.Therefore, convolutional neural networks are widely used in image and video recognition, speech recognition, and natural language processing. The architecture of convolution neural network consists of various layers which convert the raw input pixels into a class score.

Input Image

For more details, see "Learn About Convolutional Neural Networks".

You can train CNNs from scratch, by transfer learning, or by feature extraction. You can then use the trained network for classification or regression applications.

For more details on training CNNs, see "Pretrained Deep Neural Networks" .

For more details on deep learning, training process, and CNNs, see Deep Learning Onramp.

# **Deep Learning Processor**

# **Deep Learning Processor IP Core Architecture**

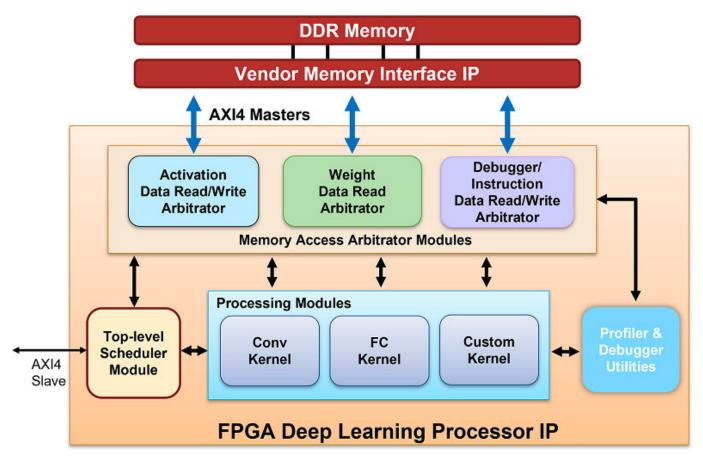

Deep Learning HDL Toolbox provides a target-independent generic deep learning processor IP core that you can deploy to any custom platform. You can reuse the deep learning processor IP core and share it to accommodate deep neural networks that have various layer sizes and parameters. Use this deep learning processor IP core to rapidly prototype deep neural networks from MATLAB and deploy the network to FPGAs.

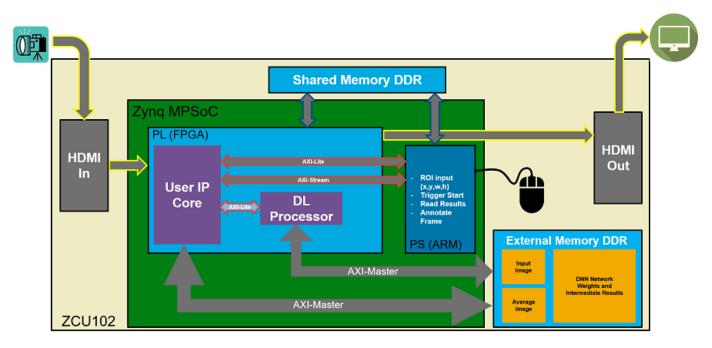

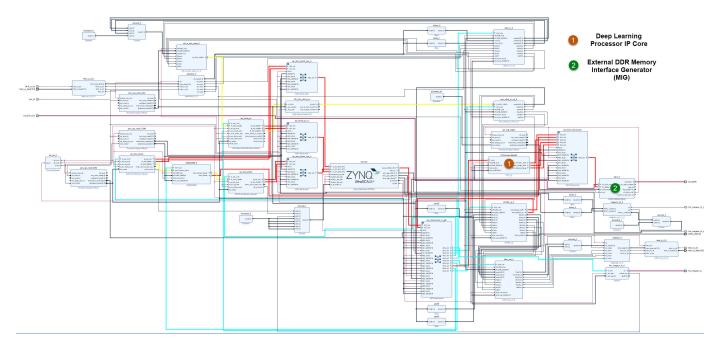

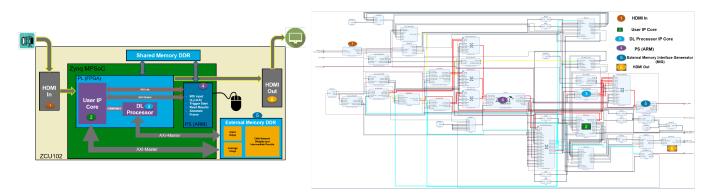

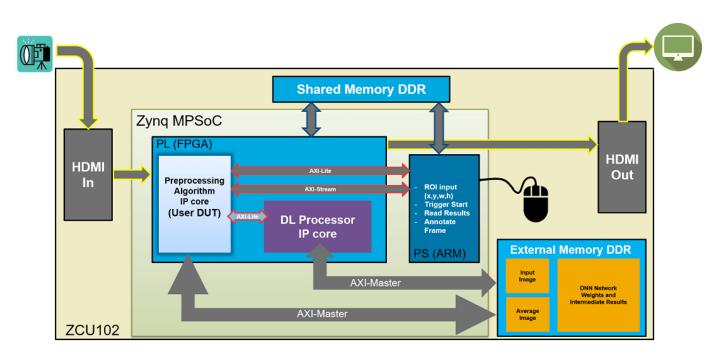

This image shows the deep learning processor IP core architecture:

To illustrate the deep learning processor IP core architecture, consider an image classification example.

#### **DDR Memory**

You can store the input images, weights, and output images in the external DDR memory. The processor consists of three AXI4 master interfaces that communicate with the external memory. You can use one of the AXI4 Master interfaces to load the input images onto the processing modules. The compile method generates the weight data. To retrieve the activation data from the DDR, see "External Memory Data Format" on page 12-9. You can write the weight data to a deployment file and use the deployment file to initialize the generated deep learning processor. For more information, see "Initialize Deployed Deep Learning Processor Without Using a MATLAB Connection" on page 5-9.

#### **Memory Access Arbitrator Modules**

The activation and weight memory access arbitrator modules use AXI Master interface to read and write weights and activation data to and from the processing modules. The profiler AXI Master interface reads and writes profiler timing data and instructions to the profiler module.

#### **Convolution Kernel**

The Conv Kernel implements layers that have a convolution layer output format. The two AXI4 master interfaces provide the weights and activations for the layer to the Conv Kernel. The Conv Kernel then performs the implemented layer operation on the input image. This kernel is generic because it can support tensors and shapes of various sizes. For a list of layers with the conv output format, see "Supported Layers" on page 7-13. For a list of the conv kernel properties, see dlhdl.ProcessorConfig.

#### **Top-Level Scheduler Module**

The top-level scheduler module schedules what instructions to run, what data to read from DDR, and when to read the data from DDR. The scheduler module acts as the central computer in a distributed computer architecture that distributes instructions to the processing modules. For example, if the network has a convolution layer, fully connected layer, and a multiplication layer the scheduler:

- Schedules the processing and data read instructions for the convolution layer and sends them to the conv kernel.

- Schedules the processing and data read instructions for the fully connected layer and sends them to the FC kernel.

- Schedules the processing and data read instructions for the multiplication layer and sends them to the custom kernel.

#### **Fully Connected Kernel**

The fully connected (FC) kernel implements layers that have a fully connected layer output format. The two AXI4 master interfaces provide the weights and activations to the FC Kernel. The FC Kernel then performs the fully-connected layer operation on the input image. This kernel is also generic because it can support tensors and shapes of various sizes. For a list of layers with FC output format, see "Supported Layers" on page 7-13. For a list of the FC Kernel properties, see dlhdl.ProcessorConfig.

#### **Custom Kernel**

The custom kernel module implements layers that are registered as a custom layer by using the registerCustomLayer method. To learn how to create, register, and validate your own custom layers, see "Register, Validate, and Deploy Custom Natural Logarithm Layer Network to FPGA" on page 8-35. For example, the addition layer, multiplication layer, resize2dlayer, and so on are implemented on the custom kernel module. For a list of layers implemented on this module, see "Supported Layers" on page 7-13. For a list of the Custom Kernel properties, see dlhdl.ProcessorConfig.

## **Profiler Utilities**

When you set the Profiler argument of the predict or predictAndUpdateState methods to on, the profiler module collects information from the kernel, such as the Conv Kernel start and stop times, FC Kernel start and stop times, and so on. The profiler module uses this information to create a profiler table with these results. For more information, see "Profile Inference Run" on page 5-4.

#### See Also

dlhdl.ProcessorConfig|compile

#### **More About**

- "Custom Processor Configuration Workflow" on page 8-2

- "Deep Learning Processor IP Core" on page 12-5

- "Use the Compiler Output for System Integration" on page 12-6

- "External Memory Data Format" on page 12-9

# **Applications and Examples**

# **MATLAB Controlled Deep Learning Processor**

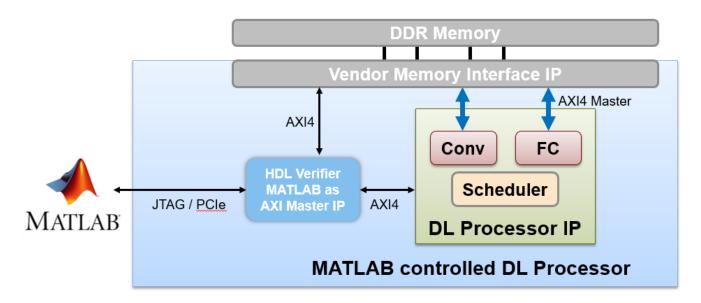

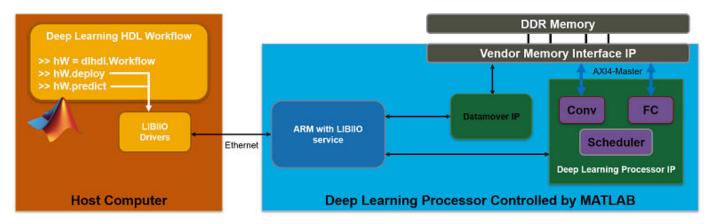

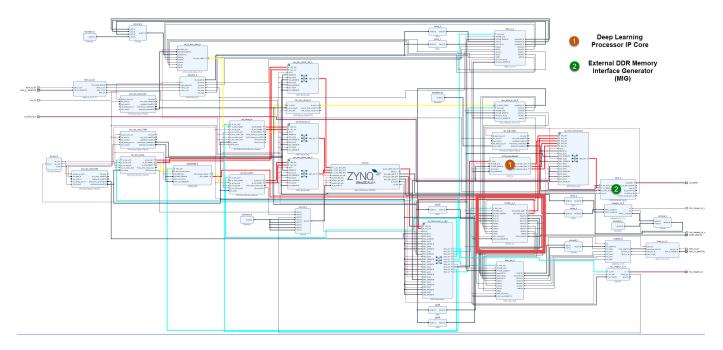

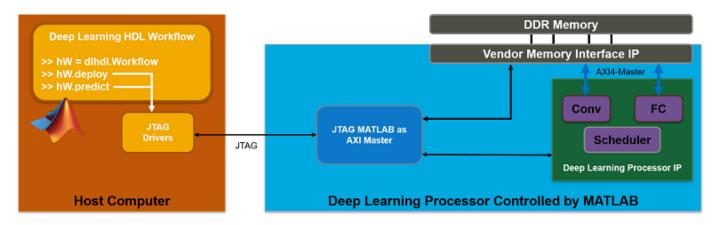

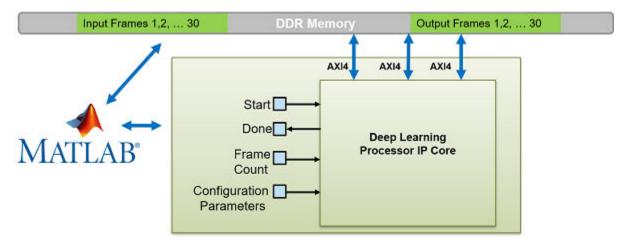

To rapidly prototype the deep learning networks on FPGAs from MATLAB, use a MATLAB controlled deep learning processor. The processor integrates the generic deep learning processor with the HDL Verifier<sup>M</sup> MATLAB as AXI Master IP. For more information on:

- Generic deep learning processor IP, see "Generate Custom Generic Deep Learning Processor IP Core" on page 12-2 .

- MATLAB as AXI Master IP, see "Set Up for AXI Manager" (HDL Verifier) .

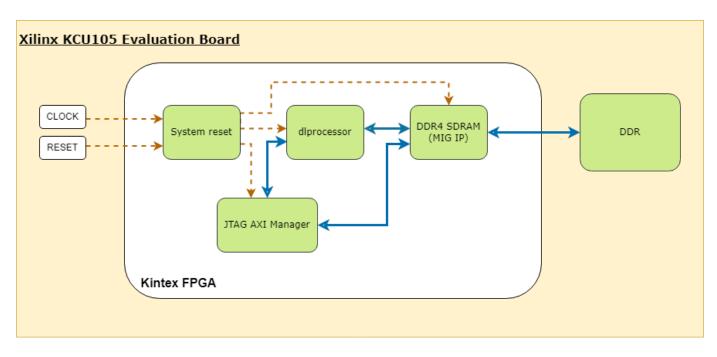

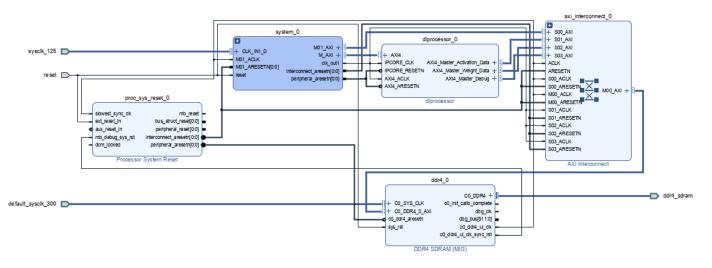

You can use this processor to run neural networks with various inputs, weights, and biases on the same FPGA platform because the deep learning processor IP core can handle tensors and shapes of any sizes. Before you use the MATLAB as AXI Master, make sure that you have installed the HDL Verifier support packages for the FPGA boards. This figure shows the MATLAB controlled deep learning processor architecture.

To integrate the generic deep learning processor IP with the MATLAB as AXI Master, use the AXI4 Slave interface of the deep learning processor IP core. By using a JTAG or PCI express interface, the IP responds to read or write commands from MATLAB. Therefore, you can use the MATLAB controlled deep learning processor to deploy the deep learning neural network to the FPGA boards from MATLAB, perform operations specified by the network architecture, and then return the predicted results to MATLAB. For example, see "Image Classification Using DAG Network Deployed to FPGA" on page 10-146.

# **Deep Learning on FPGA Overview**

- "Deep Learning on FPGA Workflow" on page 4-2

- "Deep Learning on FPGA Solution" on page 4-4

# **Deep Learning on FPGA Workflow**

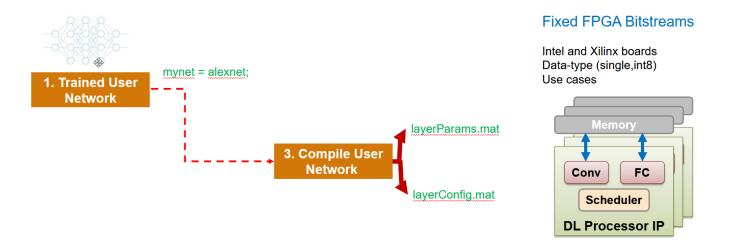

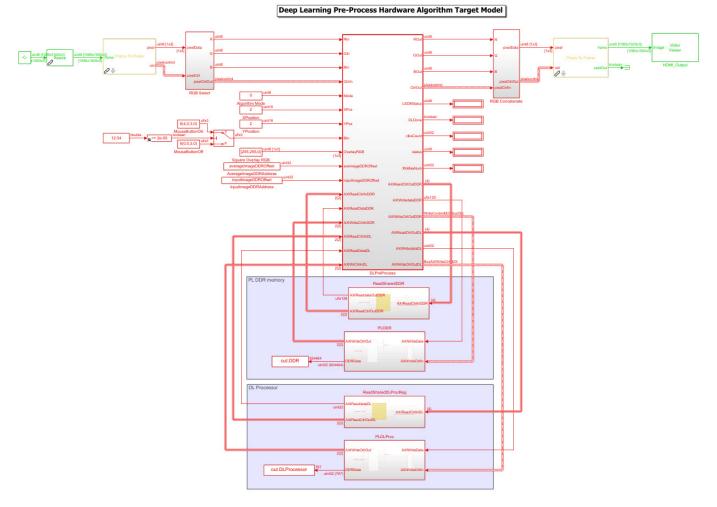

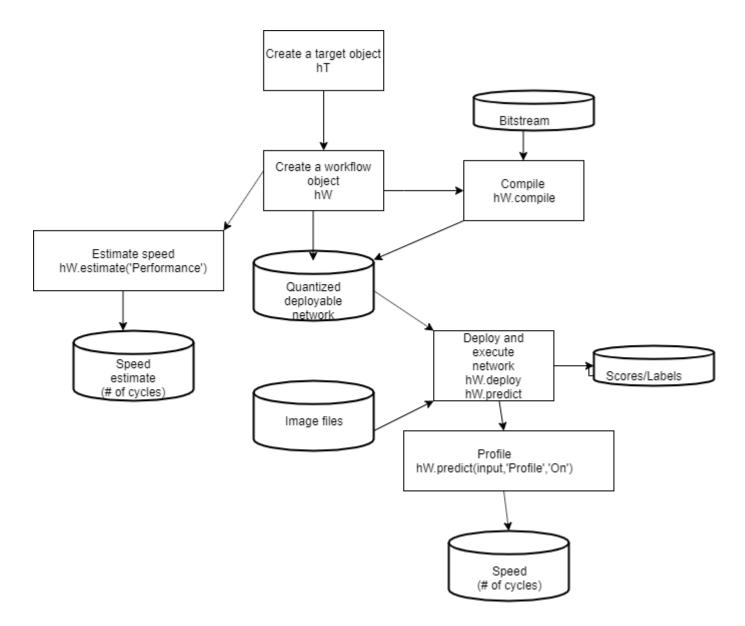

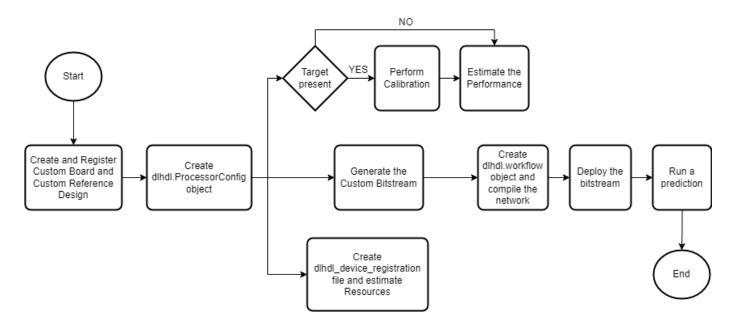

This figure illustrates deep learning on FPGA workflow.

To use the workflow:

#### **1** Load deep learning neural network

You can load the various deep learning neural networks such as Alexnet, VGG and GoogleNet onto the MATLAB framework. When you compile the network, the network parameters are saved into a structure that consists of NetConfigs and layerConfigs. NetConfigs consists of the weights and biases of the trained network. layerConfig consists of various configuration values of the trained network.

#### 2 Modify pretrained neural network on MATLAB using transfer learning

The internal network developed on the MATLAB framework is trained and modified according to the parameters of the external neural network. See also "Get Started with Transfer Learning".

#### **3** Compile user network

Compilation of the user network usually begins with validating the architecture, types of layers present, data type of input and output parameters, and maximum number of activations. This FPGA solution supports series network architecture with data types of single and int8. For more details, see **"Product Description"**. If the user network features are different, the compiler produces an error and stops. The compiler also performs sanity check by using weight compression and weight quantization.

#### 4 Deploy on target FPGA board

By using specific APIs and the NetConfigs and layerConfigs, deploying the compiled network converts the user-trained network into a fixed bitstream and then programs the bitstream on the target FPGA.

#### 5 Predict outcome

To classify objects in the input image, use the deployed framework on the FPGA board.

## See Also

"Deep Learning on FPGA Solution" on page 4-4

# **Deep Learning on FPGA Solution**

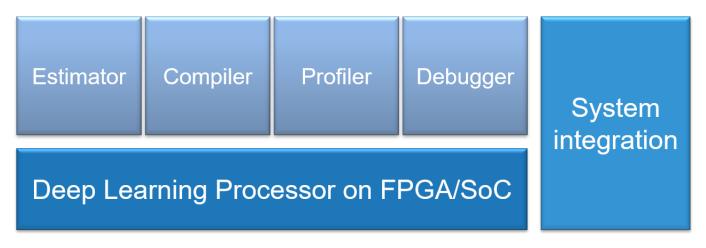

The deep learning on field programable gate array (FPGA) solution provides you with an end-to-end workflow to compile, deploy, profile and debug your custom pretrained deep learning networks. You can also generate a custom deep learning processor IP core that you can integrate into your custom reference design.

This figure shows the MATLAB based deep learning on FPGA solution.

The workflow is:

- Generate the external memory address map by using the compile function.

- Retrieve the network layer latency and overall network performance in frames per second(FPS) by using the profiler and debugger.

- Generate a custom deep learning processor IP core.

- Integrate the generated IP core into your custom reference design.

Generate the external memory address map by using the compiler. Retrieve the network layer latency and overall network performance in frames per second (FPS) by using the profiler and debugger. Generate a custom deep learning processor IP core and integrate the generated IP core into your custom reference design.

#### Advantages of Deep Learning on FPGA

FPGAs offer several advantages over a graphics processing unit (GPU) for deep learning applications.

- High performance by providing high throughput and low latency.

- Low power consumption by enabling you to fine-tune the hardware to your desired application.

- Cost effective because you can integrate additional capabilities on the same chip, which also saves costs and board space.

#### **Deep Learning on FPGA Workflows**

Based on your goals, use the information in this table to choose your workflow.

| Goal                                                                                                                             | Workflow                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Run a pretrained series network on your target FPGA board.                                                                       | "Prototype Deep Learning Networks on FPGA<br>and SoC Devices" on page 5-2          |

| Obtain the performance of your pretrained series<br>network for a preconfigured deep learning<br>processor.                      | "Estimate Performance of Deep Learning<br>Network" on page 8-3                     |

| Customize the deep learning processor to meet your resource utilization requirements.                                            | "Estimate Resource Utilization for Custom<br>Processor Configuration" on page 8-10 |

| Generate a custom deep learning processor for your FPGA.                                                                         | "Generate Custom Bitstream" on page 9-2                                            |

| Learn about the benefits of quantizing your pretrained series networks.                                                          | "Quantization of Deep Neural Networks" on page 11-2                                |

| Compare the accuracy of your quantized<br>pretrained series networks against your single<br>data type pretrained series network. | "Validation" on page 11-15                                                         |

| Run a quantized pretrained series network on your target FPGA board.                                                             | "Code Generation and Deployment" on page 11-<br>18                                 |

# **Workflow and APIS**

- "Prototype Deep Learning Networks on FPGA and SoC Devices" on page 5-2

- "Profile Inference Run" on page 5-4

- "Multiple Frame Support" on page 5-7

- "Initialize Deployed Deep Learning Processor Without Using a MATLAB Connection" on page 5-9

# **Prototype Deep Learning Networks on FPGA and SoC Devices**

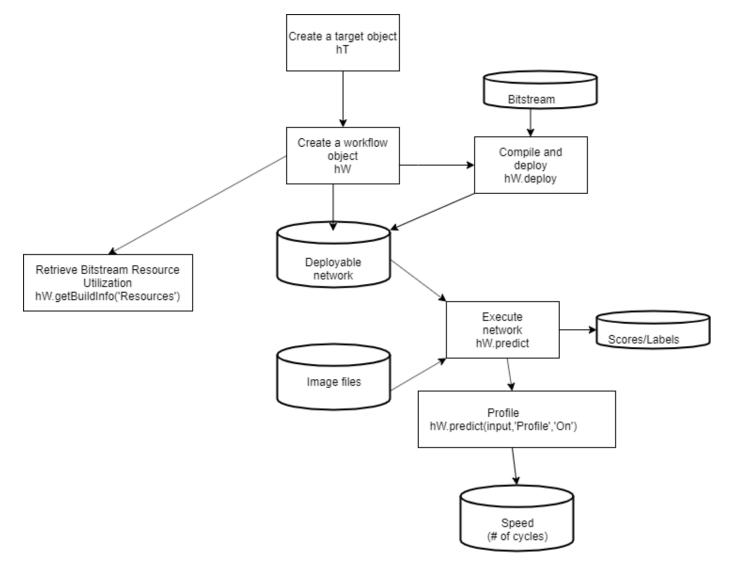

To prototype and deploy your custom series deep learning network, create an object of class dlhdl.Workflow. Use this object to:

- Compile and deploy the deep learning network on specified target FPGA or SoC board by using the deploy function.

- Retrieve the bitstream resource utilization by using the getBuildInfo function.

- Execute the deployed deep learning network and predict the classification of input images by using the predict function.

- Calculate the speed and profile of the deployed deep learning network by using the predict function.

This workflow illustrates deploying your deep learning network to the FPGA boards.

#### See Also

dlhdl.Workflow|dlhdl.Target

#### More About

• "Get Started with Deep Learning FPGA Deployment on Xilinx ZCU102 SoC" on page 10-6

# **Profile Inference Run**

This example shows how to retrieve the prediction and profiler results for the ResNet-18 network. View the network prediction and performance data for the layers, convolution module and fully connected modules in your pretrained deep learning network.

1 Create an object of class Workflow by using the dlhdl.Workflow class.

See, "Create Workflow Object by using Property Name Value Pairs".

2 Set a pretrained deep learning network and bitstream for the workflow object.

See, "Create Workflow Object by using Property Name Value Pairs".

- 3 Create an object of class dlhdl.Target and specify the target vendor and interface. See, dlhdl.Target.

- **4** To deploy the network on a specified target FPGA board, call the deploy method for the workflow object. See, deploy.

- 5 Call the predict function for the workflow object. Provide an array of images as the InputImage parameter. Provide arguments to turn on the profiler. See "Classify Images on an FPGA Using a Quantized DAG Network".

The labels classifying the images are stored in a structure struct and displayed on the screen. The performance parameters of speed and latency are returned in a structure struct.

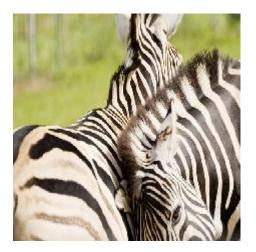

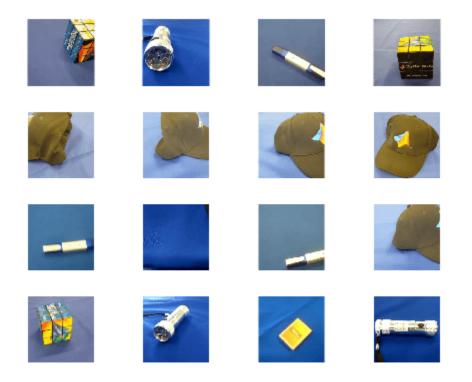

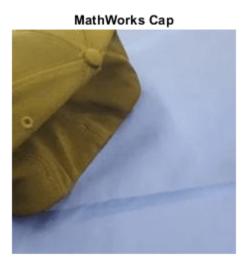

Use this image to run this code:

```

snet = resnet18;

hT = dlhdl.Target('Xilinx','Interface','Ethernet');

hW = dlhdl.Workflow('Net',snet,'Bitstream','zcul02_single','Target',hT);

hW.deploy;

image = imread('zebra.jpeg');

inputImg = imresize(image, [224, 224]);

imshow(inputImg);

[prediction, speed] = hW.predict(single(inputImg),'Profile','on');

[val, idx] = max(prediction);

snet.Layers(end).ClassNames{idx}

```

### Finished writing input activations.

### Running single input activations.

|                   | LastFrameLatency(cycles)   | LastFrameLatency(seconds) | FramesNum | Total Latency | Frames/s |

|-------------------|----------------------------|---------------------------|-----------|---------------|----------|

| Network           | 23659630                   | 0.10754                   | 1         | 23659630      | 9.3      |

| conv1             | 2224115                    | 0.01011                   | T         | 23039030      | 9.0      |

| pool1             | 572867                     | 0.00260                   |           |               |          |

| res2a branch2a    |                            | 0.00200                   |           |               |          |

| res2a branch2b    |                            | 0.00442                   |           |               |          |

| res2a             | 209312                     | 0.00095                   |           |               |          |

| res2b branch2a    |                            | 0.00442                   |           |               |          |

| res2b_branch2b    |                            | 0.00442                   |           |               |          |

| res2b             | 209736                     | 0.000442                  |           |               |          |

| res3a branch2a    |                            | 0.00340                   |           |               |          |

| res3a branch2b    |                            | 0.00411                   |           |               |          |

| res3a branch1     | 538763                     | 0.00245                   |           |               |          |

| res3a             | 104750                     | 0.00048                   |           |               |          |

| res3b branch2a    |                            | 0.00411                   |           |               |          |

| res3b_branch2b    |                            | 0.00411                   |           |               |          |

| res3b             | 104886                     | 0.00048                   |           |               |          |

| res4a branch2a    |                            | 0.00221                   |           |               |          |

| res4a branch2b    |                            | 0.00400                   |           |               |          |

| res4a branch1     | 486429                     | 0.00221                   |           |               |          |

| res4a             | 52628                      | 0.00024                   |           |               |          |

| res4b branch2a    |                            | 0.00400                   |           |               |          |

| res4b branch2b    |                            | 0.00400                   |           |               |          |

| res4b             | 52478                      | 0.00024                   |           |               |          |

| res5a branch2a    |                            | 0.00480                   |           |               |          |

| res5a branch2b    |                            | 0.00935                   |           |               |          |

| res5a branch1     | 1056510                    | 0.00480                   |           |               |          |

| res5a             | 26170                      | 0.00012                   |           |               |          |

| res5b branch2a    |                            | 0.00935                   |           |               |          |

| res5b branch2b    |                            | 0.00935                   |           |               |          |

| res5b             | 26381                      | 0.00012                   |           |               |          |

| pool5             | 71405                      | 0.00032                   |           |               |          |

| fc1000            | 216155                     | 0.00098                   |           |               |          |

| * The clock frequ | ency of the DL processor i | c. 220MHz                 |           |               |          |

Deep Learning Processor Profiler Performance Results

\* The clock frequency of the DL processor is: 220MHz

The profiler data returns these parameters and their values:

- LastFrameLatency(cycles) Total number of clock cycles for previous frame execution.

- Clock frequency Clock frequency information is retrieved from the bitstream that was used to deploy the network to the target board. For example, the profiler returns \* The clock frequency of the DL processor is: 220MHz. The clock frequency of 220 MHz is retrieved from the zcu102\_single bitstream.

- LastFrameLatency(seconds) Total number of seconds for previous frame execution. The total time is calculated as LastFrameLatency(cycles)/Clock Frequency. For example the conv\_module LastFrameLatency(seconds) is calculated as 2224115/(220\*10^6).

- FramesNum Total number of input frames to the network. This value will be used in the calculation of Frames/s.

- Total Latency Total number of clock cycles to execute all the network layers and modules for FramesNum.

- Frames/s Number of frames processed in one second by the network. The total Frames/s is calculated as (FramesNum\*Clock Frequency)/Total Latency. For example the Frames/s in the example is calculated as (1\*220\*10^6)/23659630.

#### See Also

dlhdl.Target|dlhdl.Workflow|predict

#### **More About**

• "Prototype Deep Learning Networks on FPGA and SoC Devices" on page 5-2

• "Profile Network for Performance Improvement" on page 10-47

# **Multiple Frame Support**

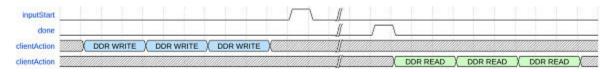

Deep Learning HDL Toolbox supports multiple frame mode enabling you to write multiple images into the double data rate (DDR) memory and read back multiple results at the same time. To improve the performance of your deployed deep learning networks, use multiple frame mode.

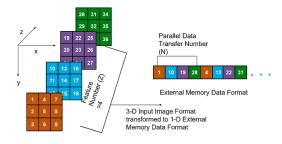

#### **Input DDR Format**

To format input images to meet the multiple frame input DDR format, you must have:

- The start address of the input data for the DDR

- The DDR offset for a single input image frame

This information is automatically generated by the **compile** method. For more information on the generated DDR address offsets, see "Use the Compiler Output for System Integration" on page 12-6.

You can also specify the maximum number of input frames as an optional argument in the compile method. For more information, see "Generate DDR Memory Offsets Based On Number of Input Frames".

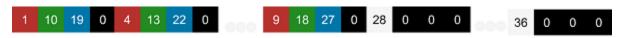

This graphic shows the format of the input area of the DDR for multiple input images.

#### **Output DDR Format**

To retrieve the results for multiple image inputs from the output area of the DDR, you must have:

- The start address of the output area of the DDR

- The DDR offset of a single result

The output results must be formatted as a multiple of the FC output feature size. The information and formatting are generated by the **compile** method. For more information on the generated DDR address offsets, see "External Memory Address Map" on page 12-6.

This graphic shows the formatting of the output area of the DDR memory.

# startAddr

padded to be multiple of FC thread number

## Manually Enable Multiple Frame Mode

After the deep learning network has been deployed, you can manually enable the multiple frame mode by writing the number of frames through a network configuration (NC) port. To manually enter the multiple frame mode at the MATLAB command line enter:

dnnfpga.hwutils.writeSignal(1, dnnfpga.hwutils.numTo8Hex(addrMap('FrameCount')),15,hT);

addrMap('FrameCount') returns the AXI register address for FrameCount, 15 is the number of images, and hT represents the dlhdl.Target class that contains the board definition and board interface definition. For more information about the AXI register addresses, see "Deep Learning Processor IP Core Report" on page 12-14.

#### See Also

dlhdl.Target|dlhdl.Workflow|compile

#### **More About**

• "Prototype Deep Learning Networks on FPGA and SoC Devices" on page 5-2

# Initialize Deployed Deep Learning Processor Without Using a MATLAB Connection

Generate a file that has instructions to communicate with the deployed deep learning processor IP core by using Deep Learning HDL Toolbox. Initialize the deployed deep learning processor IP core without a MATLAB connection by using a utility to parse and execute the instructions in the generated file.

#### Prerequisites

• Deep Learning HDL Toolbox Support Package for Intel® FPGA and SoC Devices

or Deep Learning HDL Toolbox Support Package for Xilinx® FPGA and SoC Devices

• Set up a secure digital (SD) card by using the guided SD card setup. For Intel boards, see "Guided SD Card Set Up" (Deep Learning HDL Toolbox Support Package for Intel FPGA and SoC Devices). For Xilinx boards, see "Guided SD Card Set Up" (Deep Learning HDL Toolbox Support Package for Xilinx FPGA and SoC Devices).

#### **Generate File**

To generate a file that has the instructions to program and initialize the generated deep learning processor IP configuration, set the deployment target to File by using the Target method of the dlhdl.Workflow object. For example, this code generates a dlhdl.Workflow object that has the ResNet-18 convolutional neural network as the network, zcu102\_single as the target bitstream, and deploys the instructions to a file that is called zcu102socinitdata.dln.

```

hTarget = dlhdl.Target('Xilinx',Interface = 'File', Filename = 'zcu102socinitdata.dln');

hW = dlhdl.Workflow(Network = resnet18, Bitstream = 'zcu102_single', Target = hTarget);

hW.compile;

hW.deploy;

```

When you use the deploy method of the dlhdl.Workflow object, and the interface option for dlhdl.Target is set to File, the dlhdl.Workflow object and associated instructions are written to the file whose name is in Filename.

When you do not enter the file name for the dlhdl.Target object, the name of the created file is the bitstream name. For example, in this code the generated file name is zcu102\_single.dln.

```

hTarget = dlhdl.Target('Xilinx',Interface = 'File');

hW = dlhdl.Workflow(Network = resnet18, Bitstream = 'zcu102_single', Target = hTarget);

hW.compile;

hW.deploy;

```

#### **Generated File Structure**

The generated file is a binary file that consists of:

- A header section that contains information such as the date and time the file was generated, Deep Learning HDL Toolbox version, DDR address range, and so on.

- A start of data (SOD) section that indicates the start of instructions to read and write data.

- Data section that has AXI read and write transactions.

- An end of data command (EOD) that marks the end of the file.

#### **Header Section Information**

This table lists the information available in the file header section. Strings are null terminated and uint32 data types are stored in reverse byte order. When your script reads uint32 data types, read the data from right to left. For example, 0xa0000000 is stored in the generated files as 00 00 00 A0.

| Field                                                                    | Data Type | Example Information       |  |

|--------------------------------------------------------------------------|-----------|---------------------------|--|

| File version                                                             | string    | 'MWDLNV2'                 |  |

| Date and time                                                            | string    | '25-Oct-2021 12:44:03'    |  |

| Deep Learning HDL Toolbox<br>name                                        | string    | Deep Learning HDL Toolbox |  |

| Deep Learning HDL Toolbox<br>version                                     | string    | '1.2'                     |  |

| Deep Learning HDL Toolbox<br>release information                         | string    | 'R2022a'                  |  |

| Deep Learning HDL Toolbox<br>date                                        | string    | '30-Sep-2021'             |  |

| Deep learning processor base<br>address                                  | uint32    | 0xa0000000                |  |

| Deep learning processor<br>address range                                 | uint32    | 0×00010000                |  |

| DDR memory base address                                                  | uint32    | 0×8000000                 |  |

| DDR memory address range                                                 | uint32    | 0×2000000                 |  |

| Target device platform                                                   | string    | 'Xilinx'                  |  |

| Device tree node name for deep<br>learning processor IP core<br>transmit | string    | 'mwipcore_dl0:mmrw0'      |  |

| Device tree node name for deep<br>learning processor IP core<br>receive  | string    | 'mwipcore_dl0:mmrd0'      |  |

| Device tree node name for DDR<br>memory transmit                         | string    | 'mwipcore_ddr0:mm2s0'     |  |

| Device tree node name for DDR<br>memory receive                          | string    | 'mwipcore_ddr0:s2mm0'     |  |

This image shows the header information section of the generated file.

0000000h: 4D 57 44 4C 4E 56 30 32 00 32 39 2D 4F 63 74 2D ; MWDLNV02.29-Oct-00000010h: 32 30 32 31 20 30 39 3A 31 37 3A 33 33 00 44 65 ; 2021 09:17:33.De 00000020h: 65 70 20 4C 65 61 72 6E 69 6E 67 20 48 44 4C 20 ; ep Learning HDL 0000030h: 54 6F 6F 6C 62 6F 78 00 31 2E 32 00 28 52 32 30 ; Toolbox.1.2.(R20 0000040h: 32 32 61 29 00 33 30 2D 53 65 70 2D 32 30 32 31 ; 22a).30-Sep-2021 00000050h: 00 00 00 A0 00 00 01 00 00 00 80 00 00 00 ; .....€... 00000060h: 20 58 69 6C 69 6E 78 00 6D 77 69 70 63 6F 72 65 ; Xilinx.mwipcore 0000070h: 5F 64 6C 30 3A 6D 6D 77 72 30 00 6D 77 69 70 63 ; \_dl0:mmwr0.mwipc 0000080h: 6F 72 65 5F 64 6C 30 3A 6D 6D 72 64 30 00 6D 77 ; ore\_dl0:mmrd0.mw 00000090h: 69 70 63 6F 72 65 5F 64 64 72 30 3A 6D 6D 32 73 ; ipcore\_ddr0:mm2s 00000080h: 30 00 6D 77 69 70 63 6F 72 65 pF 64 64 72 30 3A ; 0.mwipcore\_ddr0: 00000080h: 73 32 6D 6D 30 00 53 4F 44 00 57 52 44 00 57 52 ; s2mm0.SOD.WRD.WR

#### **Data Section**

After the header section, each block starts with a three-letter command, listed in this table:

| Field | Туре   | Notes           |

|-------|--------|-----------------|

| SOD   | string | Start of data   |

| EOD   | string | End of data     |

| TXT   | string | Text field only |

| WRD   | string | Data to write   |

| RDD   | string | Data to read    |

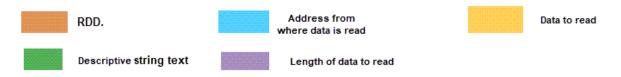

#### **Read Data Command**

After detecting the SOD command, check for read commands. The read data command appears in the generated file when you are waiting for a done flag from the deep learning processor. When the read command is executed:

- A while loop is started.

- A read is executed from a single register.

The read command and while loop end when the value of the data read from the register is equal to the value of the data in the data-to-read section of the read command.

The read data command follows this format:

- 'RDD.', a null terminated string indicating start of the read command.

- 'Text description.', a null terminated string that indicated the address from where the data is read and length of the data to be read.

- Hexadecimal representation of the register address from where data is read. This data is specified as a uint32 data type.

- Hexadecimal representation of the length of data to be read. This data is specified as a uint32 data type. The length data is the number of 32-bit data packets to be read. For example, a length value of one indicates one 32-bit data packet to read.

- Hexadecimal representation of the data to be read. This data is specified as a uint32 data type.

In the generated file, uint32 data types are stored in reverse byte order. When your script reads uint32 data types, read the data from right to left. For example, 0xa0000184 is stored in the generated files as 84 01 00 A0.

This image shows a read instruction in the generated file and the structure of the read data command. RDD.RD@ADDR:0xa0000184 Length:1. 0xa0000184 0x00000001 0x00000001.

| 00003570h: | 01 | 00 | A0 | 01 | 00 | 00 | 00 | 01 | 00 | 00 | 00 | 52 | 44 | 44 | 00 | 52 | ; |                   |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|-------------------|

| 00003580h: | 44 | 40 | 41 | 44 | 44 | 52 | ЗА | 20 | 30 | 78 | 61 | 30 | 30 | 30 | 30 | 31 | ; | D@ADDR: 0xa00001  |

| 00003590h: | 38 | 34 | 2C | 20 | 4C | 65 | 6E | 67 | 74 | 68 | ЗA | 20 | 31 | 00 | 84 | 01 | ; | 84, Length: 1.,,. |

| 000035a0h: | 00 | AØ | 01 | 00 | 00 | 00 | 01 | 00 | 00 | 00 | 57 | 52 | 44 | 00 | 57 | 52 | ; |                   |

|            |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   | -                 |

RDD.RD@ADDR: 0xa0000184, Length: 1.0xa0000184 0x000000010x00000001

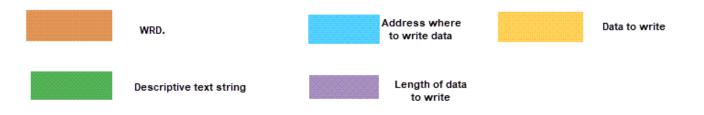

#### Write Data Command

After detecting the SOD command, check for write commands.

The write data command follows this format:

- 'WRD.', a null terminated string indicating start of the write command.

- 'Text description.', a null terminated string that indicated the address from where the data is read and length of the data to be read

- Hexadecimal representation of the register address where data is to be written. This data is specified as a uint32 data type.

- Hexadecimal representation of the length of data to write. This data is specified as a uint32 data type. The length data is the number of 32-bit data packets to write. For example, a length value of 36 indicates 36 32-bit data packets to write. When there are N data packets to write, the write data format in the generated file after the text description field is address data, length data, data packet 1, data packet 2,..., and data packet N.

- Hexadecimal representation of the data to write. This data is specified as a uint32 data type.

In the generated file, uint32 data types are stored in reverse byte order. When your script reads uint32 data types, read the data from right to left. For example, 0xa0000184 is stored in the generated files as 84 01 00 A0.

This image shows a write instruction in the generated file and the structure of the write data command. WRD.WR@ADDR:0x81800000 Len:36. 0x81800000 0x00000024 0x00000084....0x000000003. In this example, there are 36 data packets to write. The first data packet is 0x00000084 and the last data packet is 0x00000003.

| 00003a30h: | A0         | 01         | 00 | 00 | 00 | 00 | 00 | 00 | 00         | 57 | 52 | 44         | 00         | 57         | 52 | 40         | ; |                  |

|------------|------------|------------|----|----|----|----|----|----|------------|----|----|------------|------------|------------|----|------------|---|------------------|

| 00003a40h: | 41         | 44         | 44 | 52 | ЗA | 20 | 30 | 78 | 38         | 31 | 38 | 30         | 30         | 30         | 30 | 30         | ; | ADDR: 0x81800000 |

| 00003a50h: | 20         | <b>4</b> C | 65 | 6E | ЗA | 20 | 33 | 36 | 00         | 00 | 00 | 80         | 81         | 24         | 00 | 00         | ; | Len: 36€ \$      |

| 00003a60h: | 00         | 84         | 00 | 00 | 00 | 00 | 02 | 00 | 00         | 00 | 00 | 10         | 00         | 00         | 00 | 08         | ; | • ,,             |

| 00003a70h: | <b>Ø</b> 8 | 20         | 00 | 01 | 00 | 8C | 00 | 00 | 00         | F2 | 00 | 00         | 00         | 00         | 00 | <b>Ø</b> 8 | ; | Θ                |

| 00003a80h: | <b>Ø</b> 8 | 20         | 00 | 01 | 00 | 8C | 00 | 00 | 00         | F2 | 00 | 00         | 00         | 00         | 00 | <b>Ø</b> 8 | ; | Θ                |

| 00003a90h: | <b>Ø</b> 8 | 20         | 00 | 01 | 00 | 8C | 00 | 00 | 00         | F2 | 00 | 00         | 00         | 00         | 00 | <b>Ø</b> 8 | ; | Θ                |

| 00003aa0h: | <b>Ø</b> 8 | 20         | 00 | 01 | 00 | 8C | 00 | 00 | 00         | F2 | 00 | 00         | 00         | 84         | 00 | 00         | ; | Θ"               |

| 00003ab0h: | 00         | 00         | 02 | 00 | 00 | 00 | 00 | 10 | 00         | 00 | 00 | <b>0</b> 8 | <b>Ø</b> 8 | 20         | 00 | 01         | ; |                  |

| 00003ac0h: | 00         | 8C         | 00 | 00 | 00 | F2 | 00 | 00 | 00         | 00 | 02 | 00         | 00         | 00         | 00 | 00         | ; | .Θ               |

| 00003ad0h: | 00         | 00         | 00 | 00 | 00 | 05 | 00 | 00 | 00         | 00 | 00 | 00         | 00         | <b>Ø</b> 8 | 80 | 00         | ; | €.               |

| 00003ae0h: | 00         | 80         | 00 | 00 | 00 | 00 | 00 | 04 | <b>Ø</b> 8 | 00 | 01 | 00         | 00         | 03         | 00 | 00         | ; | .€               |

| 00003af0h: | 00         | 57         | 52 | 44 | 00 | 57 | 52 | 40 | 41         | 44 | 44 | 52         | ЗA         | 20         | 30 | 78         | ; | .WRD.WR@ADDR: 0x |

#### WRD.WR@ADDR: 0x81800000 Len: 36.0x818000000x000000240x00000084......0x00000003

# Initiate Deployed Deep Learning Processor IP Core

To initiate the deployed deep learning processor IP core, create a script to parse the generated file and extract the instructions to program the deep learning processor IP core. The script must perform these actions:

- **1** Take the generated file as an input and open the generated file.

- 2 Extract the header information.

- **3** Detect the start of data (SOD) command. Once the SOD command is detected:

- Read data by extracting the address, length of data to be read, and data to read information from the read packet structure. Use the readmemory function with the address and length as input arguments.

- Write data by extracting the write data address and data to write information from the write packet structure. Use the writememory function with the address and data to write as input arguments.

- 4 Detect the end of data (EOD) command and close the generated file.

# See Also

dlhdl.Target|dlhdl.Workflow|compile|deploy

# **Related Examples**

• "Deploy Simple Adder Network by using MATLAB Deployment Script and Deployment Instructions File" on page 10-223

# Fast MATLAB to FPGA Connection Using LIBIIO/Ethernet

# LIBIIO/Ethernet Connection Based Deep Learning Network Deployment

## In this section...

"Ethernet Interface" on page 6-2

"LIBIIO/Ethernet Performance" on page 6-2

# **Ethernet Interface**

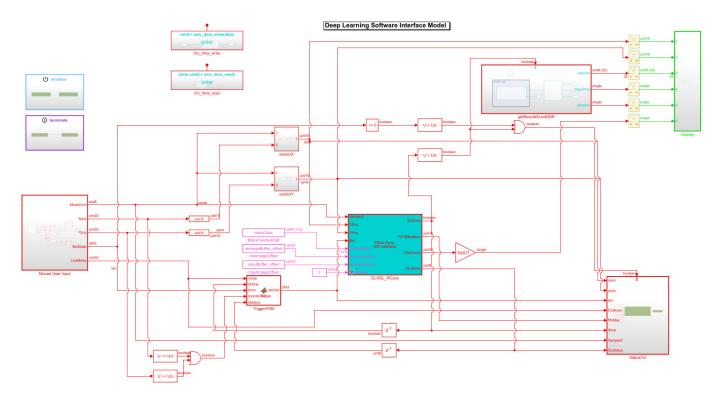

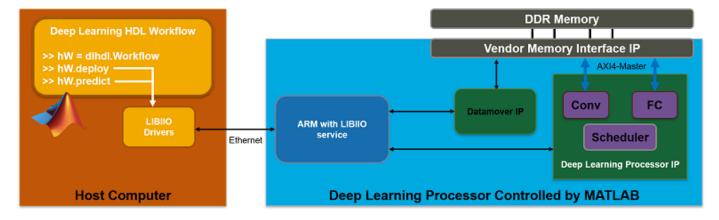

The Ethernet interface leverages an ARM processor to send and receive information from the deployed deep learning network running on the FPGA. The ARM processor runs on a Linux operating system. You can use the Linux operating system services to interact with the FPGA. When you use the Ethernet interface, the bitstream is downloaded to the SD card. The bitstream is persistent through power cycles and is reprogrammed each time the FPGA is turned on. The ARM processor is configured with the correct device tree when the bitstream is programmed.

To communicate with the design running on the FPGA, MATLAB leverages the Ethernet connection between the host computer and ARM processor. The ARM processor runs a LIBIIO service, which communicates with a Datamover IP in the FPGA design. You use the Datamover IP for fast data transfers between the host computer and FPGA, which is useful when prototyping large deep learning networks that have long transfer times over JTAG. The ARM processor generates the read and write transactions to access memory locations in the onboard memory and deep learning processor.

This figure shows the high-level architecture of the Ethernet interface.

You can configure your dlhdl.Workflow object hardware interface to use an Ethernet connection at the time of the workflow object creation. For more information, see "Create Target Object That Has an Ethernet Interface and Set IP Address".

# LIBIIO/Ethernet Performance

The improvement in performance speed of JTAG compared to LIBIIO/Ethernet is listed in this table.

| Transfer Speed | JTAG | IIO | Speedup |

|----------------|------|-----|---------|

|----------------|------|-----|---------|

| Write Transfer Speed       | 225 kB/s | 33 MB/s | Approximately 150x |

|----------------------------|----------|---------|--------------------|

| <b>Read Transfer Speed</b> | 162 kB/s | 32 MB/s | Approximately 200x |

dlhdl.Target

# **More About**

• "Accelerate Prototyping Workflow for Large Networks by Using Ethernet" on page 10-82

# **Networks and Layers**

# Supported Networks, Layers, Boards, and Tools

# In this section...

"Supported Pretrained Networks" on page 7-2

"Supported Layers" on page 7-13

"Supported Boards" on page 7-31

"Third-Party Synthesis Tools and Version Support" on page 7-31

"Image Input Layer Normalization Hardware Implementation" on page 7-31

# **Supported Pretrained Networks**

Deep Learning HDL Toolbox supports code generation for series convolutional neural networks (CNNs or ConvNets). You can generate code for any trained CNN whose computational layers are supported for code generation. For a full list, see "Supported Layers" on page 7-13. You can use one of the pretrained networks listed in the table to generate code for your target Intel or Xilinx FPGA boards.

| Networ<br>k | Networ<br>k<br>Descrip<br>tion                     | Туре              |                                                                                                                                                                                                                           | ata Type (<br>j Bitstrea                                                                                    |                                                                                                             | INT8 dat<br>Shipping                                                                                                                                                                                                      |                                                                                                             | Applicat<br>ion<br>Area |                    |

|-------------|----------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|

|             |                                                    |                   | ZCU102                                                                                                                                                                                                                    | ZC706                                                                                                       | Arria10<br>SoC                                                                                              | ZCU102                                                                                                                                                                                                                    | ZC706                                                                                                       | Arria10<br>SoC          | Classific<br>ation |

| AlexNet     | AlexNet<br>convoluti<br>onal<br>neural<br>network. | Series<br>Network | No. To<br>use the<br>bitstrea<br>m,<br>enable<br>the<br>LRNBloc<br>kGenera<br>tion<br>property<br>of the<br>processo<br>r<br>configur<br>ation for<br>the<br>bitstrea<br>m and<br>generate<br>the<br>bitstrea<br>m again. | kGenera<br>tion<br>property<br>of the<br>processo<br>r<br>configur<br>ation for<br>the<br>bitstrea<br>m and | kGenera<br>tion<br>property<br>of the<br>processo<br>r<br>configur<br>ation for<br>the<br>bitstrea<br>m and | No. To<br>use the<br>bitstrea<br>m,<br>enable<br>the<br>LRNBloc<br>kGenera<br>tion<br>property<br>of the<br>processo<br>r<br>configur<br>ation for<br>the<br>bitstrea<br>m and<br>generate<br>the<br>bitstrea<br>m again. | kGenera<br>tion<br>property<br>of the<br>processo<br>r<br>configur<br>ation for<br>the<br>bitstrea<br>m and |                         | Classific<br>ation |

| LogoNet       | Logo<br>recogniti<br>on<br>network<br>(LogoNe<br>t) is a<br>MATLAB<br>develope<br>d logo<br>identific<br>ation<br>network.<br>For more<br>informati<br>on, see<br>"Logo<br>Recognit<br>ion<br>Network | Series<br>Network | Yes | Yes | Yes | Yes | Yes | Yes | Classific<br>ation |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|--------------------|

| DigitsNe<br>t | Digit<br>classifica<br>tion<br>network.<br>See<br>"Create<br>Simple<br>Deep<br>Learning<br>Network<br>for<br>Classific<br>ation"                                                                      | Series<br>Network | Yes | Yes | Yes | Yes | Yes | Yes | Classific<br>ation |

| Lane     | LaneNet   | Series  | No. To    | Classific |

|----------|-----------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| detectio |           |         | use the   | ation     |

| n        | onal      |         | bitstrea  | bitstrea  | bitstrea  | bitstrea  | bitstrea  | bitstrea  |           |

|          | neural    |         | m,        | m,        | m,        | m,        | m,        | m,        |           |

|          | network.  |         | enable    | enable    | enable    | enable    | enable    | enable    |           |

|          | For more  |         | the       | the       | the       | the       | the       | the       |           |

|          | informati |         | LRNBloc   | LRNBloc   | LRNBloc   | LRNBloc   | LRNBloc   | LRNBloc   |           |

|          | on, see   |         | kGenera   | kGenera   | kGenera   | kGenera   | kGenera   | kGenera   |           |

|          | "Deploy   |         | tion      | tion      | tion      | tion      | tion      | tion      |           |

|          | Transfer  |         | property  | property  | property  | property  | property  | property  |           |

|          | Learning  |         | of the    |           |

|          | Network   |         | processo  | processo  | processo  | processo  | processo  | processo  |           |

|          | for Lane  |         | r         | r         | r         | r         | r         | r         |           |

|          | Detectio  |         | configur  | configur  | configur  | configur  | configur  | configur  |           |

|          | n" on     |         | ation for |           |

|          | page 10-  |         | the       | the       | the       | the       | the       | the       |           |

|          | 17.       |         | bitstrea  | bitstrea  | bitstrea  | bitstrea  | bitstrea  | bitstrea  |           |

|          |           |         | m and     |           |

|          |           |         | generate  |           |           | generate  |           | generate  |           |

|          |           |         | the       | the       | the       | the       | the       | the       |           |

|          |           |         | bitstrea  | bitstrea  | bitstrea  |           | bitstrea  | bitstrea  |           |

|          |           |         | m again.  |           |

| VGG-16   | VGG-16    | Series  | No.       | No.       | Yes       | Yes       | No.       | Yes       | Classific |

|          |           | Network | Network   |           |           |           | Network   |           | ation     |

|          | onal      |         | exceeds   | exceeds   |           |           | exceeds   |           |           |

|          | neural    |         | PL DDR    | FC        |           |           | FC        |           |           |

|          | network.  |         | memory    | module    |           |           | module    |           |           |

|          | For the   |         | size      | memory    |           |           | memory    |           |           |

|          | pretrain  |         |           | size.     |           |           | size.     |           |           |

|          | ed        |         |           |           |           |           |           |           |           |

|          | VGG-16    |         |           |           |           |           |           |           |           |

|          | model,    |         |           |           |           |           |           |           |           |

|          | see       |         |           |           |           |           |           |           |           |

|          | vgg16.    |         |           |           |           |           |           |           |           |

| VGG-19   | VGG-19    | Series  | No.       | No.       | Yes       | Yes       | No.       | Yes       | Classific |

|          |           | Network | Network   |           |           |           | Network   |           | ation     |

|          | onal      |         | exceeds   | exceeds   |           |           | exceeds   |           |           |

|          | neural    |         | PL DDR    | FC        |           |           | FC        |           |           |

|          | network.  |         | memory    | module    |           |           | module    |           |           |

|          | For the   |         | size      | memory    |           |           | memory    |           |           |

|          | pretrain  |         |           | size.     |           |           | size.     |           |           |

|          | ed        |         |           |           |           |           |           |           |           |

|          | VGG-19    |         |           |           |           |           |           |           |           |

|          | model,    |         |           |           |           |           |           |           |           |

|          | see       |         |           |           |           |           |           |           |           |

|          | vgg19.    |         |           |           |           |           |           |           |           |

| Darknet-<br>19              | Darknet-<br>19<br>convoluti<br>onal<br>neural<br>network.<br>For the<br>pretrain<br>ed<br>darknet-<br>19<br>model,<br>see<br>darknet<br>19.                                                                                                                                                | Network | Yes | Yes | Yes | Yes | Yes | Yes | Classific<br>ation                                                 |

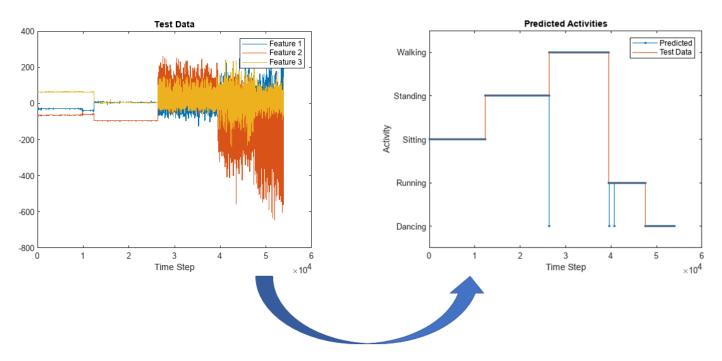

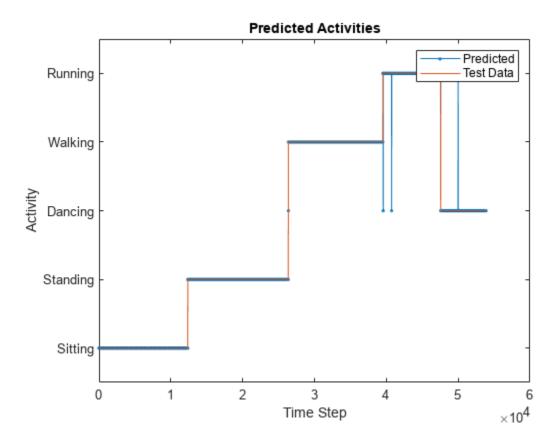

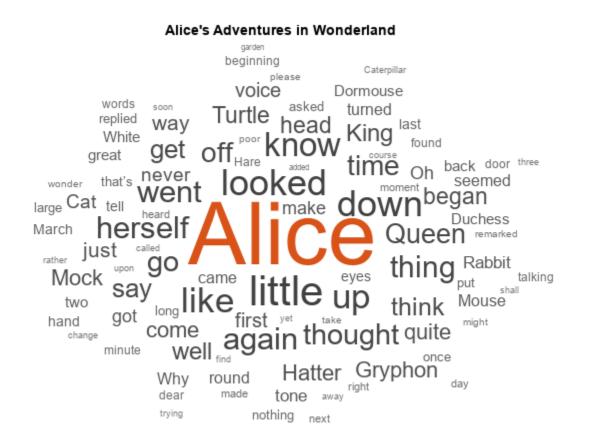

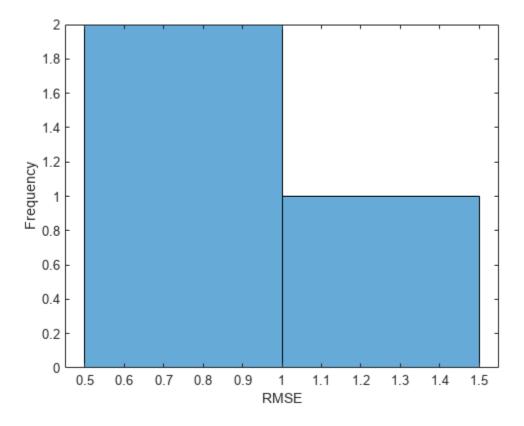

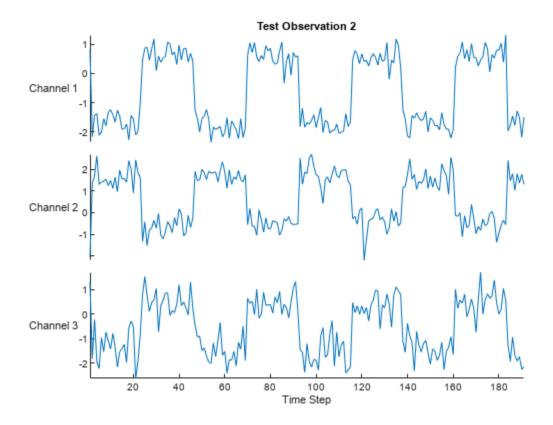

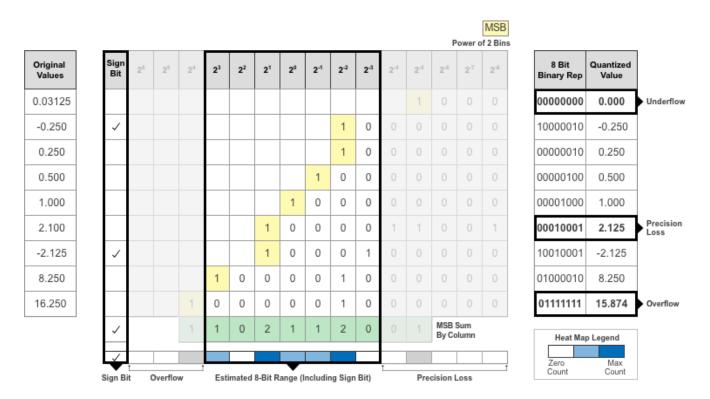

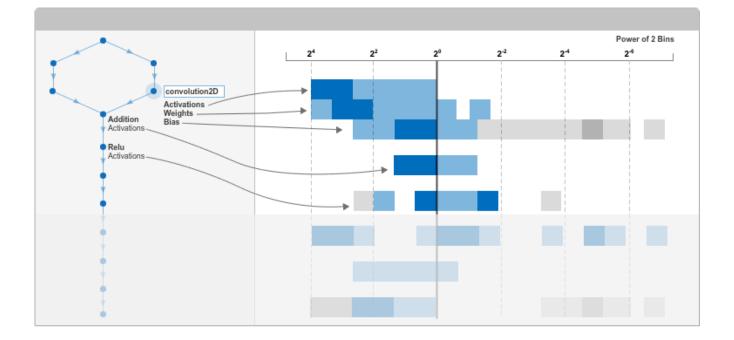

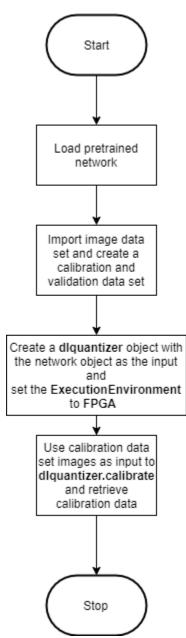

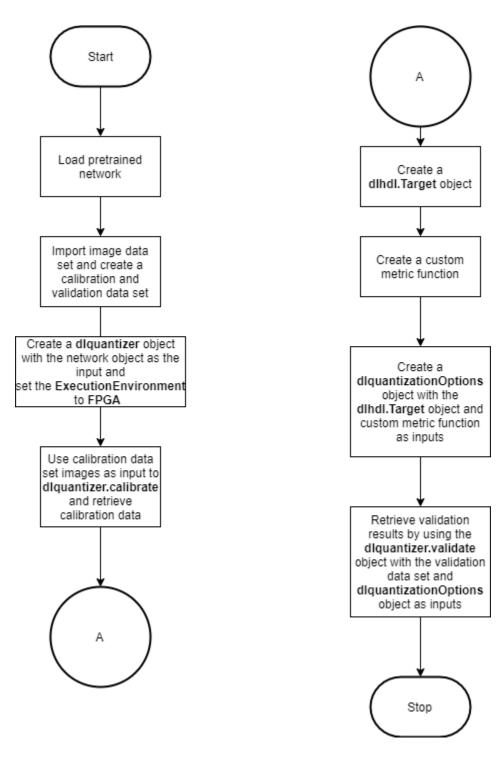

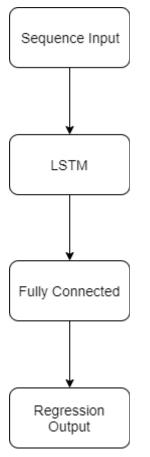

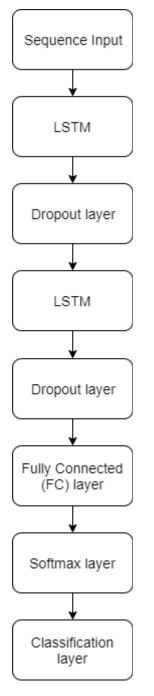

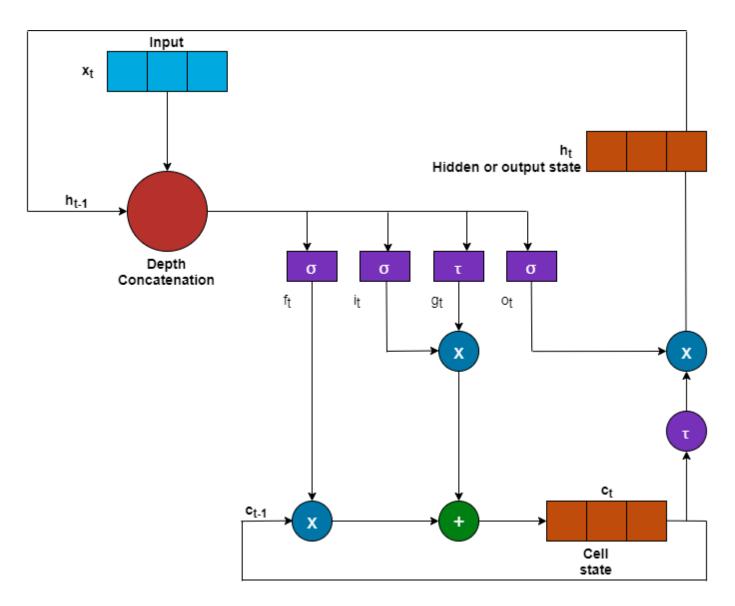

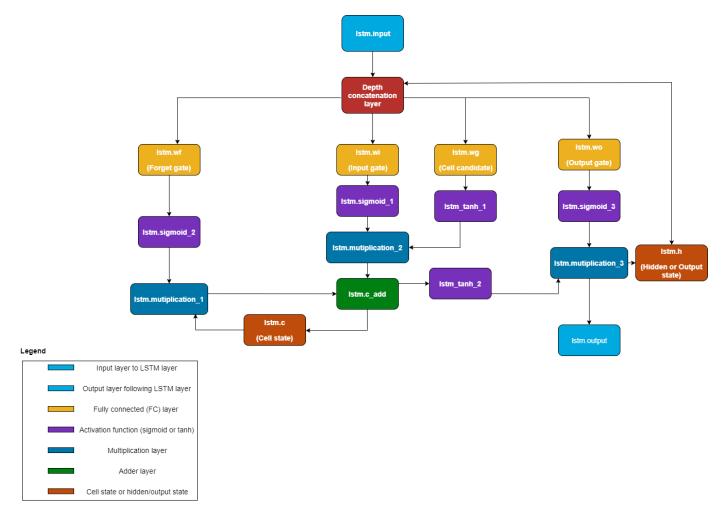

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------------|